在当今数字化高速发展的时代,芯片几乎渗透到我们生活的每一个角落。智能手机、智能家居、车载电子、工业自动化、AI服务器……这些“智慧大脑”的核心都离不开一颗颗精密的集成电路。而这些芯片是如何从设计概念变为真实的硅片?其背后功不可没的就是 EDA(Electronic Design Automation)工具。

EDA工具就像芯片设计的“工厂流水线”,它们贯穿整个研发周期,帮助工程师在虚拟世界中搭建电路、验证功能、优化性能,从而实现高效、低成本的芯片开发。

一、EDA工具:现代芯片研发的“基石”

EDA工具并不仅仅是设计软件,它们更像是芯片产业的“数字化操作系统”。

过去,如果要设计一颗芯片,需要大量人工计算、手工画电路图,不仅耗时长,出错率也高。EDA工具出现后,设计效率提升了数百倍。例如,美国加州大学的研究表明,现代EDA技术让SoC设计周期从数年缩短到数月,单个芯片设计成本从数十亿美元降到几千万美元。这也是智能硬件、物联网设备能够快速迭代、普及的关键原因。

二、EDA工具分类与功能详解

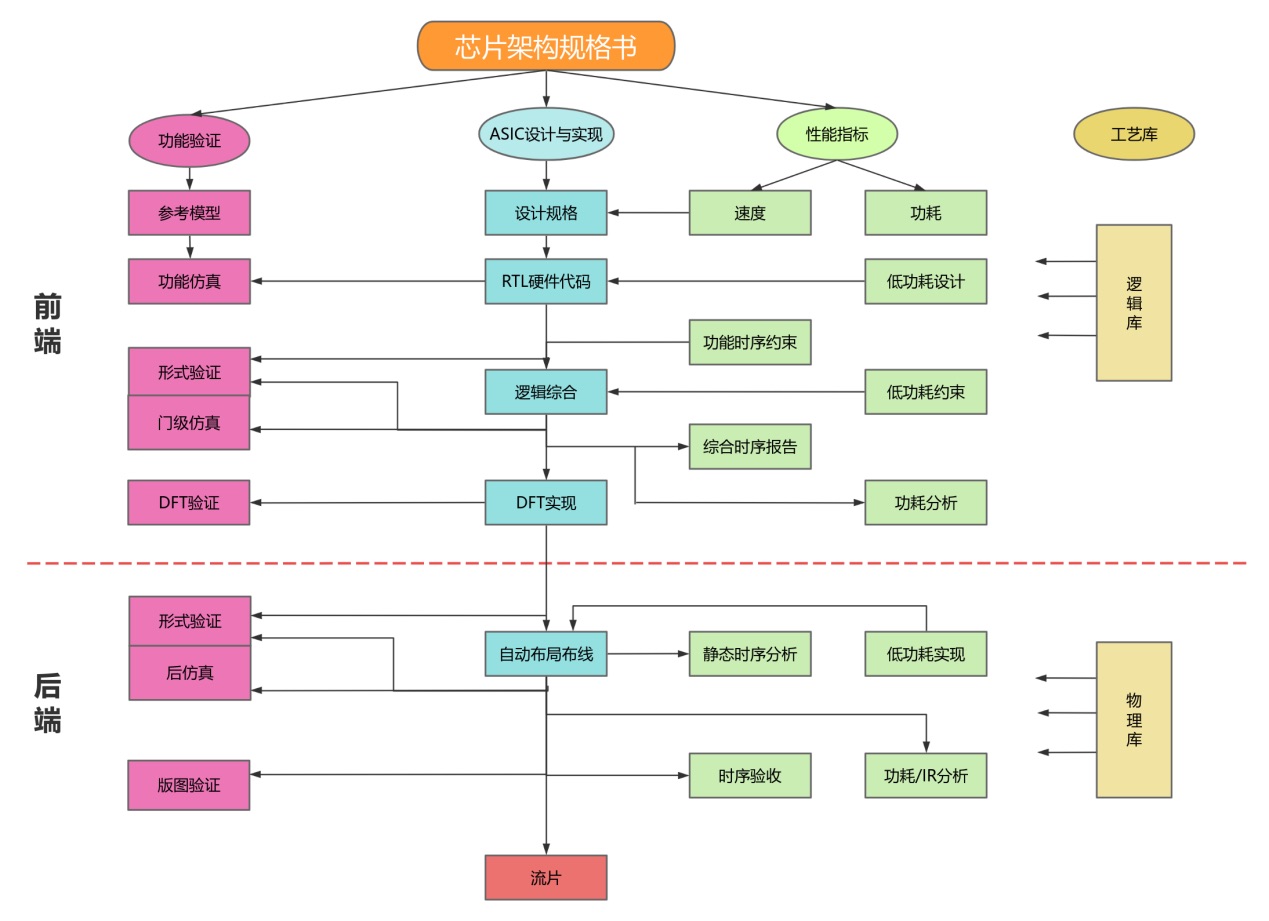

EDA工具覆盖整个芯片设计全流程,通常分为三大类:前端设计工具、后端实现工具、验证工具。下面我们逐一拆解,以便更直观了解每个环节的作用。

(一)前端设计:从概念到逻辑实现

前端设计关注的是芯片的功能逻辑,就像写一份“芯片蓝图”,描述它应该如何工作。

1. HDL编写工具:芯片设计的“编程语言”

HDL(硬件描述语言)是芯片设计的基石。常见语言有 Verilog 和 VHDL。通过这些工具,工程师可以模块化、层级化地描述电路功能。

常用工具:VisualHDL、Renoir、Composer。

实践要点:通过规范化的Code Review保证可维护性,避免后期调试成本过高。

2. 仿真工具:提前发现问题

仿真就像软件开发里的单元测试和集成测试,能在设计阶段就发现问题。常用工具有ModelSim、VCS、NC-Verilog。

工程师会在多种工作条件下对设计进行激励输入和波形观察,确保设计逻辑正确。

3. 综合工具:把代码变成电路

逻辑综合是将HDL描述转换为门级网表的过程,常用工具是Design Compiler。

优化目标:功耗(Power)、性能(Performance)、面积(Area),即PPA三要素。

4. 时序分析与形式验证:确保可靠性

PrimeTime用于检查时钟同步和建立/保持时间,避免“功能正确但时序错误”的情况;

Formality等形式验证工具则用数学证明综合前后的逻辑一致性。

(二)后端设计:从逻辑到物理版图

后端设计就像把“蓝图”变成可落地的施工图,是物理实现的关键。

1. DFT设计工具:让芯片具备自检能力

通过插入扫描链、内建自测(BIST)结构,让芯片量产后可以快速测试功能。

2. 布局布线工具PnR:确定每个单元的位置

工具如IC Compiler、Encounter,帮助确定标准单元的摆放和互连,兼顾信号时延、布线拥塞和功耗。

3. 时钟树综合CTS:保证同步运行

Clock Tree Compiler会构建优化后的时钟树,使所有寄存器接收到同步的时钟信号。

4. 寄生参数提取:确保信号完整性

提取布线电容、电阻,分析串扰影响,保证高速信号不失真。

5. 物理验证PV:确保版图可生产

Calibre等工具执行DRC(设计规则检查)和LVS(版图与原理图比对),确保设计符合代工厂的制造要求。

图4建议: 一张“后端设计流程图”,突出DFT→布局布线→CTS→寄生参数提取→物理验证的顺序关系。

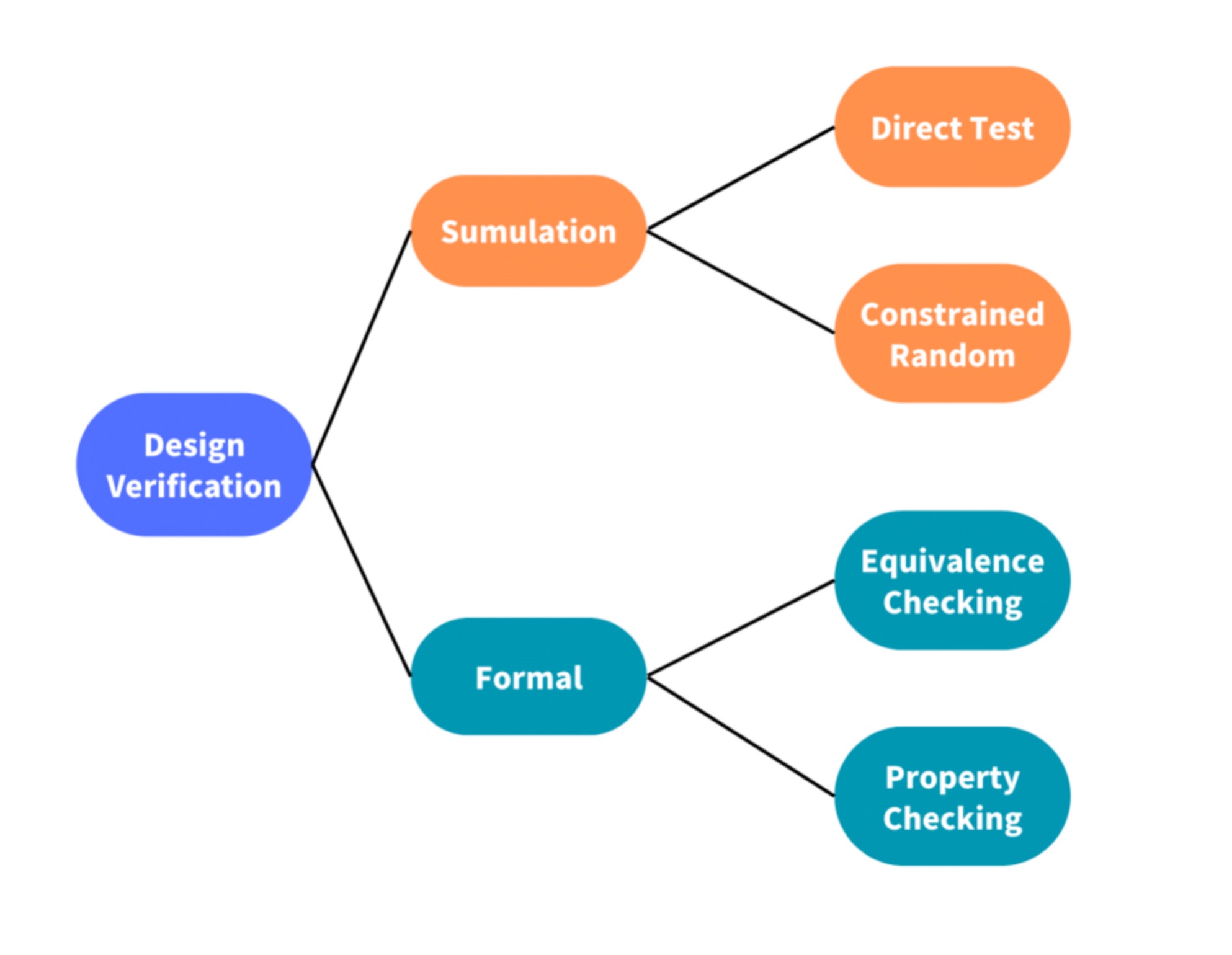

(三)验证环节:设计质量的保险丝

验证环节是芯片设计中最重要的质量保障措施之一,不仅贯穿前端,还覆盖后端完成后的各类检查。为了保证芯片在量产后能够稳定运行,验证通常要投入大量时间和人力,业内普遍认为其工作量占据整个设计周期的一半以上。验证环节可以从以下几个方面展开:

1. 前端仿真与形式验证

在完成HDL代码编写后,首先会进行仿真验证,检查逻辑功能是否符合设计规格。通过功能仿真、代码覆盖率分析以及形式验证工具(如Formality、LEC),确保综合前后的逻辑一致,避免设计逻辑在转换过程中出现偏差。

2. 后端后仿真与时序检查

当后端完成布局布线、寄生参数提取后,需要进行后仿真,将真实的寄生效应(电容、电阻、耦合等)纳入考虑,重新检查时序和信号完整性。通过工具对不同PVT角进行仿真,确认设计在极端电压、温度条件下仍然能够正常工作。

3. 验证覆盖率与回归测试

为保证设计的完整性,需要对测试用例进行覆盖率分析,确保功能、时序和异常场景都被覆盖到。发现问题后需回退设计,再进行回归测试,直到缺陷清零。这一过程会多次迭代,是耗时最长的环节之一。

4. 多维度验证扩展

随着芯片功能日益复杂,验证已不仅限于逻辑正确性,还包括低功耗模式验证、接口协议一致性验证、安全性检查、DFT结构验证等。部分项目会搭建专门的验证平台,通过仿真、硬件加速、FPGA原型验证等多种手段交叉验证,提高效率和覆盖率。

验证环节虽然耗时,但它直接决定了芯片设计的可靠性和流片成功率。高质量的验证能够显著降低返工风险,节省大量流片成本,保证产品按时推向市场。

三、EDA工具的产业链价值

虽然EDA市场规模不算大,但它是半导体产业链的“卡脖子”环节。2023年全球EDA市场规模已达145亿美元,Synopsys、Cadence、Siemens EDA占据了近八成份额。国产EDA起步较晚,但在模拟电路设计、验证工具等细分领域逐渐突破。

此外,EDA厂商主要通过软件许可和设计服务获利:

• License授权:按年或按使用次数收费,后端工具价格最高。

• 设计服务:协助客户搭建设计流程,尤其帮助初创公司加速流片。

• IP授权与版税:提供可复用的IP核,按项目收费或按出货量抽成。

四、总结与展望

EDA工具是芯片设计从“想法”到“硅片”的桥梁,它让设计迭代更快、成本更低、质量更可控。随着AI算力、汽车电子、RISC-V等新兴市场兴起,对EDA的需求将持续增长。未来,国产EDA突破也将成为半导体自主可控的重要一步。