芯片良率(Yield)常被业内人士称作“制造工艺的生命体征”。它表示在整个芯片生产流程中,从一片晶圆上切割出的所有芯片中,能正常工作的比例。良率的高低,不仅体现了生产工艺的成熟度和稳定性,也直接关系到企业的成本结构和竞争力。对于半导体制造企业来说,良率就是衡量生产线健康状况的核心指标。

一、良率的背景与意义

在半导体制造这个高度复杂的产业中,每一个细节都可能影响到最终的产品质量。良率的重要性体现在以下几个层面:

1. 提升生产效率和资源利用

晶圆的成本通常占据制造成本的大头,如果同样一片晶圆能产出更多合格芯片,意味着更高的生产效率和更低的浪费。高良率帮助企业以更少的投入获得更多的产出,从而提升整体运营效率。

2. 确保产品质量与可靠性

高良率往往意味着缺陷更少、芯片一致性更好。对于汽车电子、数据中心、医疗设备等对可靠性要求极高的应用场景,高良率直接关系到产品的寿命和稳定性。

3. 支撑技术迭代与创新

良率的提升离不开工艺优化和新技术应用。每一次工艺改进,都是制造商技术实力的体现。良率越高,意味着生产线越稳定,企业就越有精力去探索更先进的制程节点和创新设计。

4. 决定成本和市场竞争力

良率的波动直接影响单片芯片的平均成本。良率过低,意味着需要投入更多的晶圆、设备时间和人力才能满足出货需求,导致成本飙升。反之,高良率帮助企业降低售价、提升毛利率,增强市场竞争力。

二、芯片良率的基本概念与分类

良率通常用百分比来表示,其计算公式很直观:

良率 = 合格芯片数量 ÷ 总生产芯片数量 × 100%

例如,从一片晶圆切割出1000颗芯片,其中有950颗通过测试,则良率为95%。

良率不仅要看最终成品,更要在生产的各个阶段持续监控,以便及时发现问题。业内常见的良率分类方式有以下几种:

1. 按制造流程划分

• 工艺良率(Process Yield): 衡量前端制造(光刻、蚀刻、沉积等)是否稳定。

• 测试良率(Test Yield): 统计通过电学测试和功能测试的比例,反映芯片功能完整性。

• 成品良率(Final Yield): 经过封装、老化、最终测试后,能够出厂的合格芯片比例。

2. 按生产结果划分

• 初始良率(First-pass Yield): 一次性通过所有工序和测试的芯片比例,反映初次成功率。

• 最终良率(Final Yield): 包含返工或重测后的最终合格率,是交付前的“最后一道关”。

• 分阶段良率(Yield per Stage): 用于分析每一个关键工艺环节的通过率,帮助定位问题。

这种多维度的良率管理,使制造商能够精准定位薄弱环节,进行针对性改进。

三、影响芯片良率的关键因素

芯片制造过程可以类比成一条复杂的流水线,任何一个环节出问题都可能导致良率下降。主要影响因素包括工艺、材料、设备和设计。

1. 工艺因素

光刻对准误差、蚀刻深度不均、化学机械平坦化(CMP)不均匀,都会直接引入缺陷。优化工艺参数、提升设备精度、引入实时监控系统是常用的改善措施。

2. 材料因素

高纯度硅晶圆、均匀的掺杂材料是保证良率的基础。任何杂质或浓度偏差都会导致电性能异常。半导体厂商通常会与上游供应商紧密合作,严格把控材料质量。

3. 设备因素

设备的精度、稳定性和维护状况直接决定生产一致性。定期校准、预防性维护、环境控制(温度、湿度、洁净度)是保障良率的关键。

4. 设计因素

不合理的电路设计、过于紧密的布局可能导致制造难度上升。通过电子设计自动化(EDA)工具进行设计规则检查(DRC),以及在设计阶段就考虑工艺限制,可以减少后期返工。

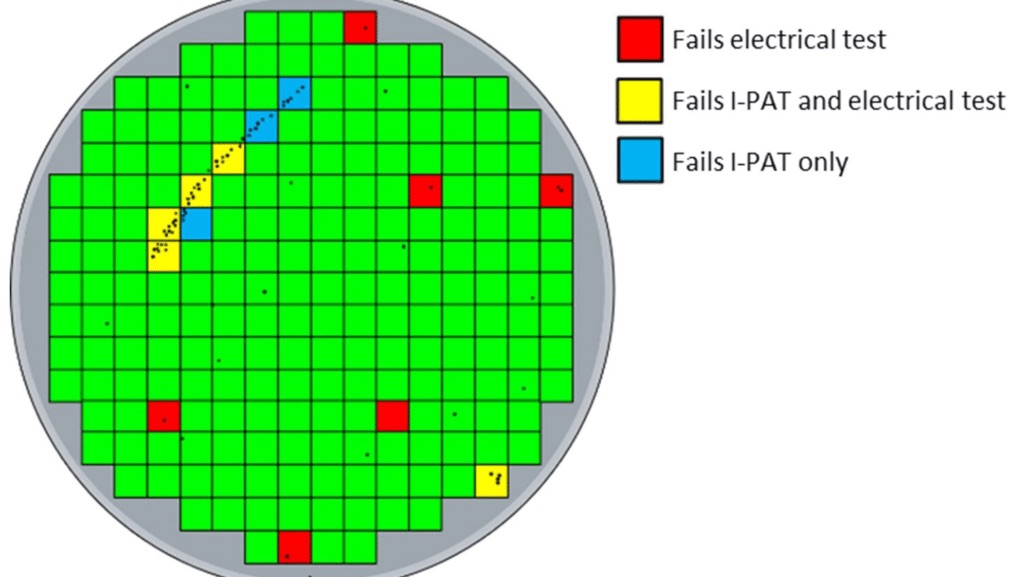

四、良率的测量与分析

良率管理不仅仅是统计数字,更需要科学的测量与深入的分析。常见方法包括:

1. 电学测试与功能测试

通过测量电压、电流、功耗等参数,判断芯片是否符合设计要求;通过模拟真实应用场景,验证芯片功能是否正常。

2. 物理检测

利用X射线、扫描电镜(SEM)、红外热成像等技术观察芯片内部结构和热分布,发现潜在缺陷和热点问题。

3. 数据分析工具

• SPC(统计过程控制): 用控制图监控生产波动,及时发现异常。

• 良率曲线分析: 追踪每批次良率变化,判断工艺是否稳定。

• 缺陷密度分布与热点分析: 定位缺陷集中区域,优化工艺参数。

• 失效分析: 对功能失效芯片进行断层扫描、显微解剖,找到根本原因。

这些分析帮助企业从“被动修复”转向“主动预防”,形成持续优化闭环。

五、先进技术在良率提升中的作用

随着制程节点不断缩小,良率提升难度加大。业内普遍采用新技术来应对挑战:

1. 极紫外光刻(EUV)

EUV光刻大幅提升图形分辨率,减少多重图形化步骤,使线路更精细、缺陷更少,从而提高初始良率和生产效率。

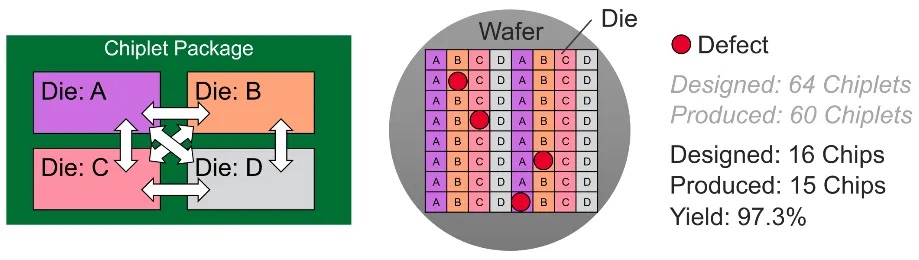

2. 芯粒技术(Chiplet)

通过将大芯片拆分为多个小芯粒独立制造,再通过高速互连封装成完整系统,降低了制造难度和缺陷概率,整体良率更容易保证。

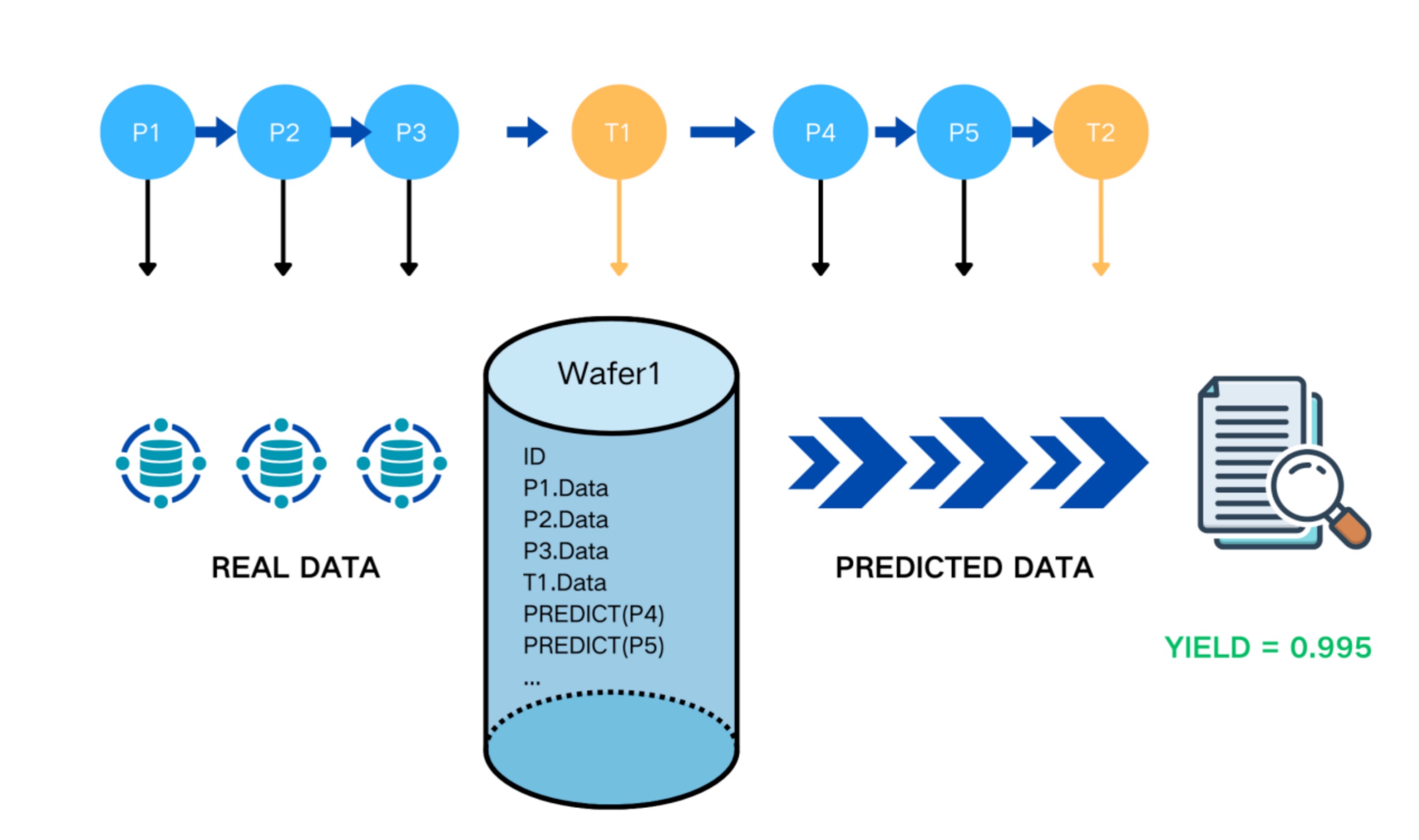

3. AI与机器学习

借助AI实时分析生产数据,识别缺陷、优化工艺参数、预测设备故障,实现预测性维护和良率预测,让生产线更智能、更高效。

六、行业案例与启示

案例1:先进制程的成功实践

某全球领先的晶圆代工厂,在5nm制程中全面导入EUV光刻,减少掩模层数,提高分辨率。同时引入机器学习模型预测缺陷点,实现生产异常的提前预警,最终在3nm节点依然保持了高良率,市场份额稳步上升。

案例2:10nm良率挑战的应对

另一家知名厂商在10nm初期遭遇大面积良率问题,通过反复工艺优化、设备升级和数据驱动的良率预测模型,逐步恢复良率并重建客户信心。

这些案例表明,良率问题并不可怕,关键是能否通过系统化的数据分析和持续改进来解决。

七、结语:良率管理是长期工程

芯片良率是企业生存和发展的生命线。它不是一蹴而就的,而是工艺优化、设计改进、材料管控、设备维护和数据分析共同作用的结果。未来,随着AI、自动化和先进工艺的深入应用,良率管理将更加智能化和可预测。能够持续提升良率的企业,才能在激烈的市场竞争中立于不败之地。